Silicon IP

Alphawave Semi offers the industry’s leading portfolio of multi-standard, connectivity IPs. These are complete silicon IP building blocks that customers license and integrate into the design of their chips.

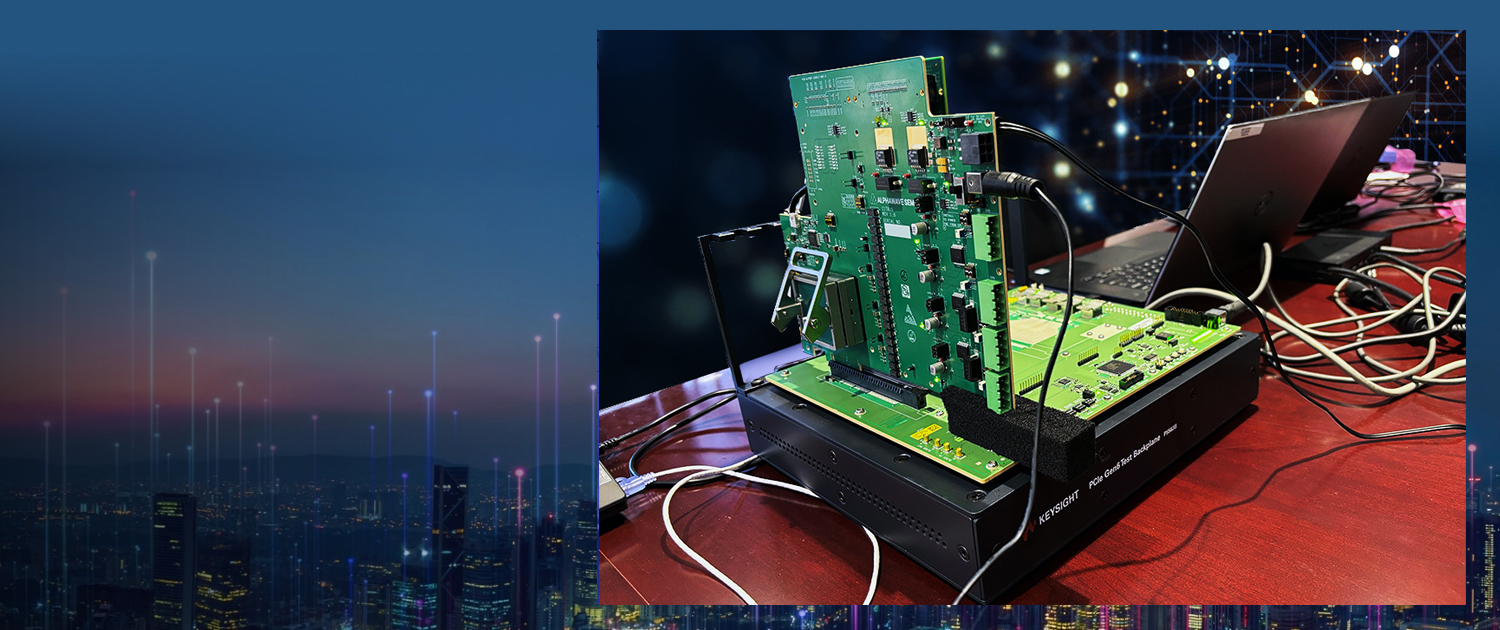

Chiplets

Alphawave Semi’s chiplet solutions build upon our industry-leading wired connectivity IP portfolio combined with our custom silicon and advanced packaging capabilities.

Custom Silicon

Alphawave Semi offers spec-to-silicon capabilities and delivers custom SOC solutions that are highly optimized for power, performance and area, providing greater design flexibility and a competitive edge.

Connectivity Products

Alphawave Semi develops industry leading PAM4 and Coherent DSP products in the most advanced technologies for all forms of data center connectivity.